Семейство Digitizer x761

производство CAEN SpA

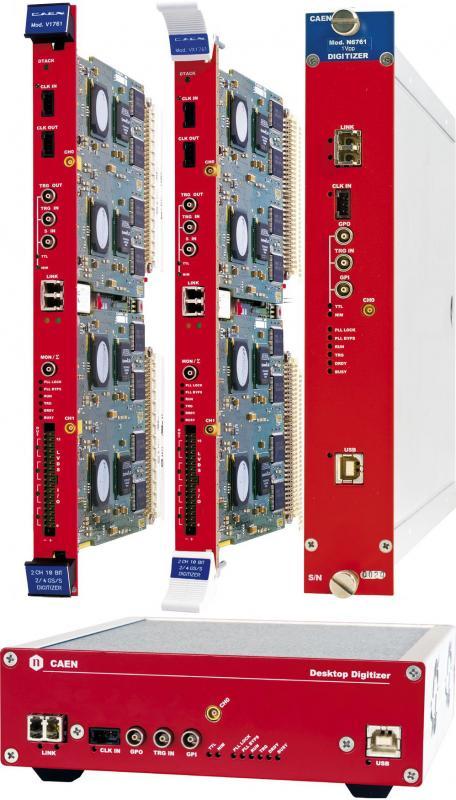

Модель x761 представляет собой семейство 10-битных и 4 ГС/с параллельных АЦП, доступных в трех форм-факторах: VME (2 входных каналов), NIM (1 входных канала) и настольный (1 входных канала).

Эти digitizer хорошо подходят для быстрых сигналов, которые поступают с сцинтилляторов, соединенных с ФЭУ или кремниевыми фотоумножителями, алмазных детекторов и других.

запросить коммерческое предложение...Основные характеристики семейства Digitizer x761

- 10-бит @ 4 ГС/с

- Аналоговые входы на коаксиальный MCX разъемах (односторонние) или разъемы AMP MODU II (дифференциальные)

- Модули VME64/VME64X (2 канала), NIM (1 канал) и настольные (1 канал)

- 1 Vpp динамический диапазон входа с программируемой регулировкой смещения постоянного тока

- Интерфейсы связи VME64/VME64X, USB и оптического интерфейса

- Функции многоплатной синхронизации

- 16 программируемых LVDS входов/выходов

- Демо-программные инструменты, программное обеспечение для управления по умолчанию и прошивка DPP, библиотеки C и LabVIEW

Возможности сбора данных позволяют использовать многобуферную организацию памяти канала. Поток данных непрерывно записывается в кольцевой буфер памяти. Когда срабатывает триггер, digitizer записывает дополнительные образцы для пост-триггера и замораживает буфер. Сбор данных может продолжаться в новом буфере без сколь угодно малого мертвого времени. Доступны два размера памяти в соответствии с различными версиями модели x761: 7,2 МС/канал или 57,6 МС/канал.

x761 снабжен FPGA, который может работать с цифровой обработкой импульсов. В дополнение к существующей прошивке CAEN может сотрудничать с заказчиками для разработки индивидуальных решений.

Общий триггерный сигнал сбора данных может быть обеспечен извне через входной разъем передней панели или через программное обеспечение. В качестве альтернативы, каждый канал может генерировать запрос триггера, когда входной импульс находится под / над программируемым порогом; запросы триггера могут использоваться либо локально по каналу (независимо от запуска с прошивкой DPP), либо обрабатываться на плате для генерации общего триггера, заставляя все разрешающие каналы одновременно получать событие (по умолчанию встроенное ПО). Триггер с одной платы может быть установлен на цифровом выходном разъеме передней панели.

x761 поддерживает многоплатформенную синхронизацию, обеспечивающую многоплатформенную систему, в которой все АЦП получаются синхронизированными с общим источником синхронизации и гарантируют выравнивание триггеров времени. После синхронизации все данные будут выровнены и согласованы на нескольких платах x761.

Физические характеристики

- Форм-фактор:

- VME64/VME64X - ширина 1U, высота 6U

- NIM - ширина 1U

- Настольный - 154 x 50 x 164 мм (Ш x В x Г)

Аналоговый вход

- 2 канала, односторонние/дифференциальные (VME)

- 1 канал, односторонний (NIM, настольный)

- Сопротивление:

- 50 Ом односторонний

- 100 Ом дифференциальный

- Разъемы:

- Односторонний MCX

- Дифференциальный AMP MODU II

- Полный диапазон шкалы:

- Пропускная способность - 1 ГГц

- Смещение - Программируемый ЦАП для регулировки смещения постоянного тока. Диапазон: ±0,5 В

Цифровая конвертация

- Разрешение - 10 бит

- Частота выборки - 4 ГС/с одновременно на каждом канале (дублируется в режиме DES)

АЦП с временной меткой

- Источник синхронизации: внутренний / внешний

- Встроенный PLL обеспечивает метку времени дискретизации АЦП из внутреннего (50 МГц осциллятора) или внешнего (разъем CLK-IN на передней панели)

Память

- 7,2 МС/канал или 57,6 МС/канал

- Буффер мультисобытий с независимым доступом для чтения и записи, делящимся на 1 ÷ 1024 буферов

- Программируемый размер события и триггер

Триггер

- Источники триггера:

- Собственный триггер: верхний / нижний порог как для генерации общего триггера

- Внешний триггер: общий для TRG-IN разъема

- Программный триггер: общий с помощью команды программного обеспечения

- Распространение триггера:

- Цифровой выход TRG-OUT (VME) / GPO (NIM и настольный)

- Метка времени триггера: 31-битный счетчик, разрешение 16 нс, диапазон 17 с

Синхронизация

- Распространение метки времени:

- Цепь Daisy (только VME) с помощью разъемов CLK-IN/CLK-OUT

- Распределение метки времени от одного ко многим из внешнего источника синхронизации

- Компенсация задержки кабеля

- Синхронизация сбора данных:

- Синхронизация Пуск/Стоп с помощью цифрового входа/выхода (вход S-IN, TRG-IN или GPI, выход TRG-OUT или GPO)

- Сброс метки времени внешнего триггера

LVDS вход/выход (только VME)

- 16 входов/выходов LVDS общего назначения, управляемых FPGA

- Занятость, готовность данных, полная память, индивидуальная настройка и другие функции могут быть запрограммированы

- Входной шаблон от модулей ввода/вывода LVDS может быть связан с каждым триггером как маркер события

Аналоговый монитор (только VME)

- 12-бит / 100 МГц ЦАП FPGA управляемый выход с четырьмя режимами работы: триггерное большинство / тестовые импульсы / занятость памяти / уровень напряжения

Интерфейсы связи

- Оптическая связь:

- Собственный протокол CAEN CONET, скорость передачи данных до 80 Мбайт/с

- Цепь Daisy: возможно подключить до 8/32 АЦП модулей к одному контроллеру оптической линии (модель A2818/A3818)

- USB (NIM и настольный, VME через мост V1718):

- Совместимость с USB 2.0

- Скорость передачи до 30 Мбайт/с

- VME:

- Совместимость с VME 64X

- Режим передачи данных: BLT32, MBLT64 (70 Мбайт/с с использованием CAEN Bridge), CBLT32/64, 2eVME, 2eSST (до 200 Мбайт/с)

Питание

- Настольный: 1,8 A при 12 В

- NIM: 3,9 A @ +6 В, 120 мА @ -6 В

- VME: 6,5 A @ +5 В, 200 мА при +12 В, 300 мА @ -12 В

VME

- WV1761CXAAAA | V1761C - 2 канала, 10 бит, 4 ГС/с Digitizer: 57,6 МС/с, EP3C16

- WV1761XAAAAA | V1761 - 2 канала, 10 бит, 4 ГС/с Digitizer: 7,2 МС/с, EP3C16

- WVX1761CXAAA | VX1761C - 2 канала, 10 бит, 4 ГС/с Digitizer: 57,6 МС/с, EP3C16

- WVX1761XAAAA | VX1761 - 2 канала, 10 бит, 4 ГС/с Digitizer: 7,2 МС/с,EP3C16

Настольный

- WDT5761XAAAA | DT5761 - 1 канал, 10 бит, 4 ГС/с Digitizer: 7,2 МС/с, EP3C16

NIM

- WN6761XAAAAA | N6761 - 1 канал, 10 бит, 4 ГС/с Digitizer: 7,2 МС/с, EP3C16